�����Ŀ���������������£���֤��·����Ϊ�������е��Ƿ�һ�¡�ʹ��Modelsim���湤�߽��в�����Modelsim��Ҫ��Quartus II���ù�����

���� Quartus II �� modelsim ����ϵ

�� �����������֮����Ҫ�� Quartus II ������ modelsim ·����Quartus II �˵�Tools ����>General����>EDA Tool Options������������ã���modelsim��C:\Modeltech_6.3g\win32 ��ͼ2��ʾ��

modelsim���ܷ��沽��

һ����������

�����ļ��У���modelsim��ѡfile�µ�change directory�������е�choose folder�Ի���������Ŀ¼·����

������������

ѡfile ��new�����project����project name����д��Ŀ���֡�

��Ŀ������붥���ļ���һ�¡�

project location �ǹ���Ŀ¼�����Լ�ѡ��

default library name��ֱ�Ӳ���Ĭ�ϵ�work����ˣ�workspace�����е�library�оͻ����work�⡣

����Ϊ���������ļ�

ѡ��add exsiting file������Ӧ��ʾ���ļ����Ӵ���projcet�У�������ƶ����ļ�.v�Լ����������ļ�.v/.vt��

�ġ������ļ�

compile�е�compile all��

�塢װ���ļ�

ѡ��library�е�work����IJ��������ļ������simulate�µ�start simulation��

������ʼ����

��workspace�µ�sim�У�ѡ������������һ���ѡadd�е�add to wave��Ȼ����simulate��ѡ��run all��

�ߡ��˳�����

simulate�е�end simulation��

ע:

1 ��ɲ�����testbench����ʼ�IJ����ͬ�ϣ���װ���ļ�ʱ��ѡ������ļ�����sim�е�add �����add to wave��

ֱ�Ӷ������źű༭���Բ��Σ��һ�Ҫ�༭���źţ�ѡ��create wave����Ȼ����run�����run all��

2 ��modelsim��ֱ��дtestbench��

����file��ѡ��new�����source�����ڲ˵�����������һ��source��Ŀ����source���¹�ѡshow language templates�������ָü����˫�����е�create testbench�������һ��create testbench wizard����work��ѡ������ļ����ٵ��next������ָ��testbench����Ҫ���뵽�Ŀ�ȣ�Ĭ�ϼ��ɣ����finish���Լ��������ݾ�ok�ˡ������ļ���Ϊ.v.

����֮��ͬǰ���轫testbench�ļ����뵽���������漴�ɡ�

Modelsim�ķ����Ϊǰ����ͺ�����������Ⱦ������һ�����ߵ�����

1 ǰ����

ǰ����Ҳ��Ϊ���ܷ��棬��ּ������֤��·�Ĺ����Ƿ�������Ҫ�����ص��Dz����ǵ�·���ӳ������ӳ٣���Ҫ����֤��·����������Ƿ�һ�¡����ۺ�FPGA��������RTL���������������ģ�������ΪRTL��������Testbench.

2 �����

�����Ҳ��Ϊʱ�������߲��ֲ��ߺ���棬��ָ��·�Ѿ�ӳ�䵽�ض��Ĺ��ջ����Ժ��ۺϿ��ǵ�·��·���ӳ������ӳٵ�Ӱ�죬��֤��·�ܷ���һ��ʱ��������������ƹ���Ĺ��̣��Ƿ����ʱ��Υ�档�������ļ�Ϊ�Ӳ��ֲ��߽���г���������ż�������Testbench����չ��ΪSDO��SDF�ı�ʱ���ļ���SDO��SDF�ı�ʱ���ļ������������ӳ٣�������ʵ�ʲ����ӳ٣��ܽϺõط�ӳоƬ��ʵ�ʹ��������һ����˵������DZ�ѡ�ģ�������ʱ����ʵ�ʵ�FPGA��������Ƿ�һ�£�ȷ����ƵĿɿ��Ժ��ȶ��ԡ�ѡ���������������ź���������档

3 Modelsim����Ļ�������

Modelsim�ķ�����Ҫ�����¼������裺

(1)�����Ⲣӳ������Ŀ¼��

(2)����ԭ���루���� Testbench����

(3)ִ�з��档

����3�������Ǵ�Ŀ�ܣ�ǰ����ͺ������ǰ��������ܽ��еģ�����modelsim���̶�ǰ�������˵�����DZ���ġ�

3.1������

��ִ��һ������ǰ�Ƚ���һ���������ļ��У�����IJ������ڴ��ļ��½��У��Է�ֹ�ļ�����������Ȼ������Modelsim����ǰ·���ĵ����ļ����£��ĵķ����ǵ�File->Change Directoryѡ��ո��½����ļ��м���ͼ��

ͼ3 �½��ļ���

��ǰ�����ʱ���Ƽ������������µ��ļ��С�

��������ʱ���� Quartus II �����ļ����»����һ���ļ��У������ļ���\simulation\modelsim��ǰ������ȷ���� Quartus II ���̣���ˣ������ٽ����µ��ļ����ˡ�

������Ǵ洢�ѱ�����Ƶ�Ԫ��Ŀ¼��modelsim �����������⣬һ���ǹ����⣬Ĭ�ϵĿ���Ϊwork,��һ������Դ�⡣Work���°�����ǰ�����������Ѿ���������ļ������Ա���ǰһ��Ҫ��һ��work�⣬����ֻ�ܽ�һ��work�⡣��Դ����work�����Ѿ������ļ���Ҫ���õ���Դ����������Դ�����кܶ࣬���DZ����ڲ�ͬ����Դ���ڡ�������Ҫ���ۺ���cycloneоƬ�е����������棬����Ҫ��һ����Ϊcyclone_ver����Դ�⡣

ӳ������ڽ��Ѿ�Ԥ����õ��ļ����ڵ�Ŀ¼ӳ��Ϊһ��modelsim��ʶ��Ŀ⣬���ڵ��ļ�Ӧ�����Ѿ�������ģ���Workspace������չ���ÿ�Ӧ���ܿ�����Щ�ļ��������û�б�������ļ��ڿ����ǿ������ġ�

���������ķ��������֡�һ�������û�����ģʽ�£���File->New->Library��������ĶԻ���ѡ��a new library and a logical mapping to it,��Library Name������Ҫ����������ƣ�Ȼ��OK����������һ���Ѿ�ӳ����¿⡣��һ�ַ�������Transcript���������������

vlib work

vmap work work

ͼ4 ���������

���Ҫɾ��ij�⣬ֻ��ѡ�иÿ��������Ҽ�ѡ��Delete���ɡ�

��Ҫע����Dz�Ҫ��modelsim�ⲿ��ϵͳ�����ֶ���������������ļ������Ҳ��Ҫmodelsim�õ���·�������ļ�����ʹ�ú��֣���Ϊmodelsim������ʶ���ֶ�����Ī������Ĵ���

3.2��д���������ļ�

�ڱ�дTestbench֮ǰ������Ƚ�Ҫ�����Ŀ���ļ����뵽�������У���Compile->Compile�� ������������ĶԻ���

ͼ5 ����Ŀ���ļ�

��Library��ѡ�����⣬�ڲ��ҷ�Χ���ҵ�Ҫ�����Ŀ���ļ�(Libraryѡ��ղŽ����Ŀ⣬���ҷ�Χѡ��Ŀ���ļ����ڵ��ļ���)��Ȼ���Compile��Done����������������vlog Counter.v����ʱĿ���ļ��Ѿ����뵽�������У���Library��չ��work������ᷢ�ָ��ļ���

����Ҫ�����Ŀ���ļ����з���ʱ��Ҫ���ļ��еĸ�����������ṩ����Դ���������벨�ν��е��ϸ��壬���ֶԼ���Դ������ļ���ΪTestbench��������̨�ļ��������Ƚ�һ��Testbench�IJ���������

����һ�����ǿ�����modelsim��ֱ�ӱ�дTestbench������modelsim���ṩ�˳��õĸ���ģ�塣���岽�����£�

�� ִ��File->New->Source->verilog������ֱ�ӵ���������ϵ��½�ͼ�꣬�����һ��verilog�ĵ��༭ҳ�棬�ڴ��ĵ���������ɱ༭����̨�ļ�����Ҫ˵��������Quartus��������ۺϵ�����ڴ˴�������ʹ�ã�����testbenchֻ��һ������Դ�����ļ���ֻҪ�����벨�ν��ж����Լ���ʾһЩ��Ҫ��Ϣ���ɣ��мDz�Ҫ��Ĺ��ڸ��ӣ���������������

�� Modelsim�ṩ�˺ܶ�Testbenchģ�壬����ֱ���ù����ÿ��Լ��ٹ���������verilog�ĵ��༭ҳ��Ŀհ״��Ҽ���Show Language TemplatesȻ������һ�����ع��̣�������ᷢ���ڸղŵ��ĵ��༭������߳�����һ��Language Templates����,����ͼ��

ͼ6 Ӧ��ģ������ Testbench�ļ�

˫��Creat Testbench�����һ������������ͼ��

ͼ7 ������

ѡ��Specify Design Unit�������£�work�������µ�Ŀ���ļ�����Next,��������Ի���

ͼ8 ����Testbench��

����ָ��Testbench�������Լ�Ҫ���뵽�Ŀ�ȣ��˴�����ʹ��Ĭ������ֱ�ӵ�Finish����ʱ��Testbench�ڻ���ֶ�Ŀ���ļ��ĸ����˿ڵĶ��廹�е��ú���������������߿����Լ���Testbench������������(��ע�͵�Ϊ���ӵ�����)��Ȼ��Ϊ.v��ʽ���ɡ�����ǰ��ķ�����Testbench�ļ�Ҳ���뵽�������С�

ͼ9 ���ɼ��ĺ��Testbench�ļ�

���������� Quartus II �ڱ�д������ Testbench ��֮�� Testbench ��Ŀ���ļ�����ͬһ���ļ����£�����ǰ��ķ����� Testbench �ļ���Ŀ���ļ������뵽��������֮��

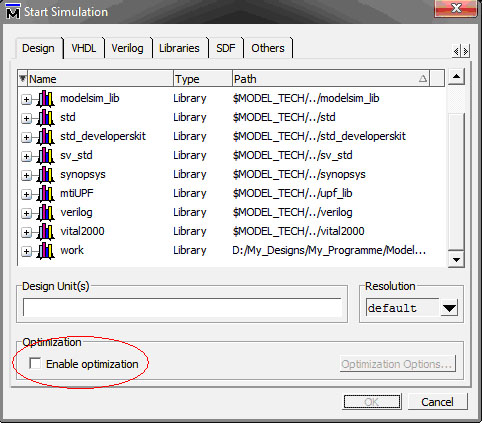

PS������ڹ�������û�и��ļ�(��Testbench�ļ�û�ж˿ڵ������)������Simulate����>Start Simulate��Ƭ��ȥ���Ż�ѡ�����ͼ��ʾ��֮�������±��룬�����ڹ��������ҵ����ļ���

ͼ10 ȥ���Ż�ѡ��

3.3ִ�з���

��Ϊ�����Ϊǰ����ͺ���棬����ֱ�˵����β�����

�� ǰ����

ǰ���棬�����˵�DZȽϼġ�����һ�������Ѿ�����Ҫ���ļ����뵽���������ˣ���������ֻ���simulate->Start Simulation���ݰ�ť �����start simulate�Ի����Design��ǩѡ��Work���µ� Testbench �ļ���Ȼ��� OK ���ɣ�Ҳ����ֱ��˫�� Testbench�ļ�Counter_tb.v����ʱ���������Ľ��档

ͼ11 start simulate

���������л�����һ��Objects���ڣ�������ʾ Testbench �ﶨ��������ź�����,��Workspace��Ҳ������һ��Sim��ǩ���Ҽ����Counter_tb.v,ѡ��Add->Add to Wave������ͼ��ʾ��Ȼ����Wave���ڣ����ھͿ��Է����ˣ�����ͼ��

ͼ12 Wave����

���������Ѿ������˴�����ĸ����źţ��� ����ʼִ�з��浽100ns,��������沨��Ҳ���������죬����ͼ��

ͼ13 ���沨��

���� �������һֱִ�У�ֱ���� ��ֹͣ���档

Ҳ������������������� run @1000

��ִ�з��浽1000ns,�����1000Ҳ�����DZ����ֵ������߿����ġ�����һ�����и�����ʱ�����ŵ�ǰ�IJ��μ���������档 ���ˣ�ǰ���沽����ɡ�

�� �����

�����Dz��õ�Cyclone ii����һ��counter�����ӡ�

�������ǰ����IJ��������ͬ��ֻ�����м���Ҫ���ӷ����(����ѡ����������IP Core���)����������ʱ�ļ��IJ��衣

������ǰ����quartus�Ѿ���Ҫ�����Ŀ���ļ����б��룬������modelsim��������Ҫ��.vo�ļ�(�����ļ�)��.sdo�ļ���ʱ���ļ�����������������������ַ�����һ����ͨ��Quartus����Modelsim��Quartus�ڱ���֮���Զ��ѷ�����Ҫ��.vo�ļ��Լ���Ҫ�ķ����ӵ�modelsim�У�������һ�����ֶ�����Ҫ���ļ��Ϳ����modelsim���з��棬���ַ����������������ܶ��ԣ���ַ���modelsim��ǿ����湦�ܡ�

�� ͨ��Quartus����Modelsim

ʹ�����ַ���ʱ����Ҫ��Quartus�������á� ������Quartus����Ҫ����Ĺ��̣���˵�����Assignments����EDA Tool settings��ѡ�����Category�е�Simulation.�����ұߵ�Tool name��ѡModelSim(Verilog),ѡ�������Run Gate Level Simulation automatically after complication.����ͼ��

ͼ14 ��Quartus��������

Quartus�еĹ�������֮����start complication��ť����ʱmodelsim���Զ���������quartus���ڵȴ�״̬��ǰ����ϵͳ�����������û�������PATHҪ���ú�modelsim��װ·��,�磺D:\Modeltech_6.3\win32�����ڴ�modelsim��Workspace��������ᷢ�ֶ��˹��������Դ�⣬����work���г�������Ҫ������ļ���Modelsim�Զ���quartus���ɵ�.vo�ļ����뵽work�⣬��������Ӧ����Դ�⡣��ͼ��ʾ��

ͼ15 Quartus II ����֮��������modelsim

�۲�⣬���Է��֣�����verilog_libs�⡢gate_work���work�⣬������"�����ļ���\simulation\modelsim"�£�ֻ��verilog_libs��gate_work�ļ��У�Ϊʲô������ȴ����һ��work���أ�����gate_work���work���ļ�������ͬ��

gate_work ����Quartus II ����֮���Զ����ɵģ���work����modelsimĬ�Ͽ⡣��ϸ�۲����·��������·����ͬ����Ϊgate_work�ļ��У���֪ modelsim �� gate_work ��ӳ�䵽 work �⡣��ˣ��ں����Ĺ����в���gate_work ����� work �ⶼ�ܵõ���ȷ�����

��д����̨����Counter_tb.v ����÷������ɵ�.vo�ļ����ڵ�Ŀ¼���Է�������Ҫ�ֶ�����ʱʹ�á���Compile�ڳ��ֵĶԻ�����ѡ��Counter_tb.v�ļ���Ȼ���Compile��ť,����������Done����ʱ��Work���л���ֲ���̨�ļ�������ͼ��ʾ��

ͼ16 ��������ļ�

���simulate->Start Simulation���ݰ�ť �����start simulate�Ի����Design��ǩѡ��Work���µ�Counter_tb.v�ļ���Ȼ����Libraries��ǩ��Search Library�е��Add��ť��ѡ���������Ҫ����Դ�⣨�����֪����Ҫѡ���ĸ��⣬������ֱ�ӵ�Compile�����ֵĴ�����ʾ��˵��Ҫ�Ŀ�����Ȼ�����ظ��������裩����ͼ��

ͼ17 ѡ���������Ҫ����Դ��

�ٵ�start simulate�Ի����SDF��ǩ���ڳ��ֵĶԻ����SDF File���ڼ���.sdoʱ���ļ�·������Apply To Region������һ����/���� �ڡ�/����ǰ���������̨�ļ���������Counter_tb���������ĺ����������̨�����е��ñ����Գ���ʱ�������Գ���������ƣ�������Ϊ��DUT��������ͼ��Ȼ���OK������۲첨����ǰ���沽����ͬ��

ͼ18 ����.sdo�ļ�

�Զ�������ֶ����������

���ַ����Ƚϼ���ΪQuartus II����Modelsim �����Գ��������Զ�������modelsim��������Ҫ��.vo�ļ�(�����ļ�)��.sdo�ļ���ʱ���ļ����⣬��������gate_work�ļ��С�verilog_libs�ļ��У�gate_work�ļ���(���Խй����⣬Ҳ���Խб����)�´�����ѱ�����ļ���verilog_libs�ļ����´���˷�������Ҫ����Դ�⣬������cycloneii_ver��(�ļ���)�����ֶ���������Ҫ�Լ�������Щ�ļ��Ϳ⡣�������¡�

�� �ֶ�����

�ֶ�������Ҫ�Լ������ļ��ͱ���⣬�����Գ�ַ���modelsimǿ��ķ��湦�ܡ�����ʱҲҪ�ȶ�quartus�������ã�������ǰ����ֻͬ�Dz�Ҫѡ��Run Gate Level Simulation automatically after complication��Ȼ������modelsim������ǰ·���ĵ�"�����ļ���\simulation\modelsim"�¡�����ͼ��ʾ��

ͼ19 ����modelsim

��Ȣ��У���������һЩ��(ʵ����verilog_libs�⡢gate_work���work��)���������Ҫ����һ���⡣�½�һ���⣬�˴�Ĭ�Ͽ���Ϊwork����ʱ��"�����ļ���\simulation\modelsim"�ļ����³�����һ��work�ļ��У�work������û��Ŀ���ļ��Ͳ����ļ�����work�ļ�����û���κ��ļ��������Ŀ�ľ��ǽ�������ļ������ڸÿ�������ڸ��ļ����¡�����֮ǰ������Ҫ���ӷ�������Ҫ����Դ��cycloneii_atoms(�õ�EP2C8)����D:\altera\90\quartus\eda\sim_libĿ¼�µ�cycloneii_atoms�ļ����Ƶ�.vo���ڵ�Ŀ¼����"�����ļ���\simulation\modelsim"�¡�

������բ��еķ�����дtestbench��ͬ������.vo���ڵ�Ŀ¼����ʱ��Compile�µ�Compile��� �����������ĶԻ�����ѡ�ļ����б��롣

ͼ20 ���������ļ�����Դ��

�������֮��work�������¶��˺ܶ��ļ���ͬ��work�ļ�����Ҳ���˺ܶ��ļ�(��)�������Ŀ�Ŀɼ�һ�ߣ�������Counter_tb�����ļ���counterĿ���ļ������simulate->Start Simulation���ݰ�ť �����start simulate�Ի�������͢����ֻ��Libraries��ǩ��Search Libraryʱ��һ��������2�һ����Libraries��ǩ��Search Library����������ͼ��

ͼ21 ѡ���������Ҫ����Դ��

����Ĺ۲첨�β����ǰ��һ����

�ġ��۲첨�ε�һЩ�����ͼ��ɡ�

4.1 �ֶ��������벨��(����)

���ڸ��ӵ�����ļ���������Լ���дtestbench�ļ����������Ծ�ȷ������ź��Լ������ź�֮���������ϵ�ȣ���߷���Ч�ʡ�

����һЩ������ļ���Ҳ�����ڲ��δ����Լ��������벨�ν��з��档���巽��������һ�work�����Ŀ������ļ�counter.v��Ȼ���create wave������wave default���ڡ�����ͼ��ʾ��

ͼ22 Add to Wave

��wave������ѡ��Ҫ�������ε��źţ�������е�CLK��Ȼ���Ҽ������ѡ��Create/Modify/Wave���������Ĵ��ڣ�

ͼ23 �������벨��

��Patterns��ѡ�����벨�ε����ͣ�Ȼ��ֱ����ұߵĴ������趨��ʼʱ�䡢��ֹʱ���Լ���λ���ٵ�Next��������Ĵ��ڣ����ǰѳ�ʼֵ��HiZ��Ϊ0��Ȼ����ʱ�����ں�ռ�ձȣ�Ȼ���Finish��

ͼ24 �������벨��

���ż��������������벨�Σ���������Ľ����ǰ����ֵĺ���ʾ�ò����ǿɱ༭�ġ�����IJ�������testbench�ı�����ķ�����ͬ ��

ͼ25 ���沨��

4.2 �۲��ض��źŲ���

��������ֻ��鿴ָ���źŵIJ��Σ�������ѡ��objects������Ҫ�۲���źţ�Ȼ����Ҽ�ѡ��Add to Wave->Selected signals,����ͼ����ô��Wave������ֻ����ѡ�е��źš�

ͼ26 �鿴�ض��źŲ���

4.3 ����͵��벨���ļ�(����)

���Ҫ���沨�δ��ڵ�ǰ�źŵķ��䣬���Ե�File->Save,�ڳ��ֵĶԻ��������ñ���·�����ļ���������ĸ�ʽΪ.do�ļ���

������뵼���Լ������IJ��Σ��������������ϸ�Ľ��ͣ�����ѡ��File->Export Waveform�ڳ��ֵĶԻ�����ѡ��EVCD File������������ü��ɡ�

���������ƵIJ���ѡ��File->Import ECVD���ɡ�

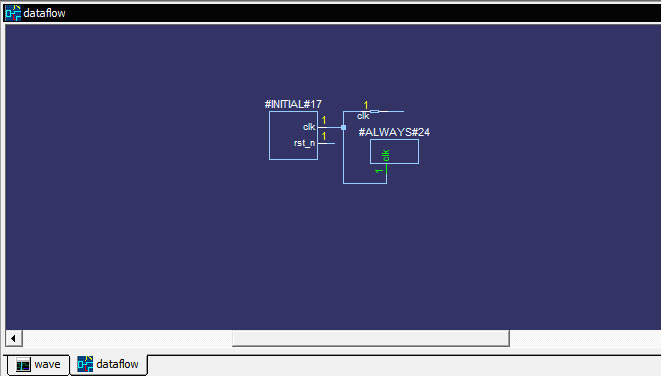

4.4 Dataflow���ڹ۲��źŲ���

���������е�View->Dataflow���Կ��������dataflow���ڣ���objects��������һ���źŵ��ô����У���ᷢ����dataflow�����г�����ղ�ѡ���ź����ڵ�ģ�飬���˫��ģ���ijһ���ţ������������������ı��ģ��������ߣ�����ͼ��

ͼ27 Dataflow����

��dataflow�����е�View->Show Wave������dataflow�����г���һ��wave���ڣ�˫�����洰���е�ijһģ�飬���������wave�����г������ģ�������������źţ�����Ѿ�ִ�й����棬��wave�����л�����ֶ�Ӧ�IJ��Σ�����ͼ��

ͼ28 Dataflow���ڹ۲���沨��

�ڲ��δ������϶��α꣬����ģ��������źŵ�ֵҲ�������α굱ǰλ�õĸı���ı䡣

���Ҫ��modelsim����ԭ����ļ������ĵ�ҳ�����Ҽ���ȡ��Read Only�������ģ��ĺ�������档��������������Ե�Simulate->End Simulation,��ֱ��������������quit -sim����ʱquartusҲ����ʾ�������б�����̡�

�塢 һЩ˵��

������testbench��ʹ��`timescale������

`timescale �DZ�����ָ���������ʱ�Ӿ��Ⱥ�ʱ�ӵ�λ�������ʽΪ

`timescale time_unit/time_precision

����time_unit����ʱ�ӵ�λ��������ģ���г��ֵ�ʱ����ֵ�ĵ�λ��time_precision����ʱ�Ӿ��ȡ�����

`timescale 1ns/100ps ��ʾʱ�ӵ�λΪ1ns��ʱ�Ӿ���Ϊ100ps��

������������ #5.22 a=1;

��ʱʱ��ֵ5.22nsӦ�ö�ӦΪ5.2ns����Ϊ����Ϊ0.1ns��

�������ж��ģ�����������`timescale������ʱģ�������Ƕ���������ģ�����Сʱ�Ӿ����ϣ���������ģ���е�ʱ�Ӷ��Զ��ػ���Ϊ����С���龫���ϡ�

��¼��

CounterԴ���룺

`timescale 1ns/100ps

module Counter (

input CLK,

input RST_N,

output [3:0] CNT

);

reg [3:0] cnt;

assign CNT = cnt;

always@(posedge CLK, negedge RST_N) begin

if (!RST_N)

cnt <= #5 4'h0;

else

cnt <= #0 cnt + 1'b1;

end

endmodule

Counter_tbԴ���룺

`timescale 1ns/100ps

module Counter_tb ;

wire [3:0] CNT ;

reg RST_N ;

reg CLK ;

Counter

DUT (

.CNT (CNT ) ,

.RST_N (RST_N ) ,

.CLK (CLK ) );

//http://wenku.baidu.com/view/cd93f34ecf84b9d528ea7a95.html

initial begin

#0 CLK = 1'b0;

RST_N = 1'b0;

#5 RST_N = 1'b1;

end

// 50MHz

always #10 CLK = ~CLK;

ϲ��

ϲ��  ��

�� �ѹ�

�ѹ� ��

�� ��

�� ����

����